# Low Power and Low Latency Memristive-Ternary Content Addressable Memory Design Using Absolute Path Search Optimization (APSO) Algorithm

Dr.K. Sharmilee, G. Rathanasabhapathy, T. Jayachandran and R. Murugasami

Abstract--- In this work, a Low Latency and low power use of memristive ternary content addressable memory (MTCAM) design is implemented for utilizing new optimization method specifically Absolute Path Search Optimization (APSO) algorithm. The outline of a proposed memory has been altered by the expansion of all validation supervisors required by the equipment usage of switching devices in the memory. In addition, aAPSO has been incorporated into real time application to permit a memory design based on full self-rule. Therefore, compared with the conventional design comprising of a switching-block and an isolated memory, this new method will prompt an imperative decrease of data searching among the memory read and write procedure. The proposed work is depicted utilizing Verilog language, synthesized and actualized utilizing Xilinx ISE suite based Field Programmable Gate Array (FPGA) devices. Synthesis results demonstrate that the proposed configuration accomplishes higher efficiency than the previous executions by decreasing area while keeping up a moderate throughput/Look Up Table (LUT) ratio. The proposed configuration is additionally more productive as far as power utilization.

*Keywords--- MTCAM- Memory, Absolute Path Search Optimization, Memristive-ternary Content Addressable Memory, Low Latency and Low Power.*

### I. INTRODUCTION

In the biological neural systems, synaptic weight representing the correlation between two neurons can be gradually strengthened or weakened by the ionic flow. This phenomenon seems similar with memristor's behaviour. Here memristor's conductance can be adjusted by the history of charge and flux through the memristor. These memristors that represent the nanoscale synaptic connections between the sending neurons (preneurons) and receiving neurons (post-neurons) can be structured as a crossbar array. This crossbar can be useful in realizing high density and power efficient neuromorphic architecture. In this section, the TCAM design is extended to MTCAM operation and compared with the cell of; a MCAM cell stores data ('0' and '1'), and searches (for '0', and '1') to perform a match/no-match operation. Ternary Content Addressable Memories (TCAMs) circuits are broadly utilized in location arrangements and packet filtering in networking applications. Elite Network Routers and the directing tables require enhanced look up execution quick and high capacity TCAMs.

Dr.K. Sharmilee, Professor, Department of ECE, Nandha Engineering College, Erode, Tamilnadu. E-mail: sharmijaisha@gmail.com G. Rathanasabhapathy, Asst. Professor, Department of ECE, Nandha Engineering College, Erode, Tamilnadu. E-mail: rathanamgrs@gmail.com

T. Jayachandran, Asst. Professor, Department of ECE, Nandha Engineering College, Erode, Tamilnadu. E-mail: jaynecdsp@gmail.com

R. Murugasami, Asso. Professor, Department of ECE, Nandha Engineering College, Erode, Tamilnadu. E-mail: murugasami.r@gmail.com

This segment presents a TCAM that utilizes memristors as a storage component. Regularly two memristors are associated in an arrangement to execute the task in customary memory and appropriate functions. This memory cell is quick and productively trims information and the memristors are broke down by different perspectives. The proposed APSO optimization based MeTCAM is simulated using Xilinx software. In the proposed system Each TCAM row stores one pattern of the highly frequent input operands and use a 6-transistor/2-memristor structure for each bit for the TCAM design.

#### **II. LITERATURE SURVEY**

For a few programs, the cache hit rate is enhanced to expanding the number of approaches to two way or four way cache [1], the past four way cache isn't noteworthy. More ways infer more simultaneous look-ups per getting to prompting more vitality per getting to a direct mapped cache utilizes just 30% of the vitality for each entrance as a four-way set related cache [2]. Most elevated conceivable associativity is required in execution decided applications. A novel configurable cache design [3] fuses three configurable cache parameters, these are arranged on setting a couple of bits in the setup register.

The cache can be designed in programming as either coordinate mapped, two-way or four-way set related while using the full limit of cache. Such a setup is achieved by utilizing a system called way link [4-6]. The method called line link [7] is utilized to design the cache line measure. A few designs for decreasing the vitality utilization in the cache are accounted for in the writing.

One of them is the dividing of the cache into a few little caches [8-10]. This outcome in the decrease of access time and the power cost per access. Another approach, filter cache [11] exchanges execution for control utilization by the filtration of cache references through a unusually little L1 cache. An L2 cache comparative in structure and size to an L1 cache is set after the filter cache for limiting the execution trouble. A particular option, specific cache ways in [12-14] renders the capacity to disable a subset of routes in a set affiliated cache among the intervals of modest cache action through the entire cache is operational for cache escalated periods.

In another approach, the regular unified data cache can be supplanted with multi particular caches. Everyone handles a distinctive sort of memory references according to their particular area qualities [15]. These selections make it conceivable to enhance as far as execution and power effectiveness[16].

#### **III. PROPOSED METHODOLOGY**

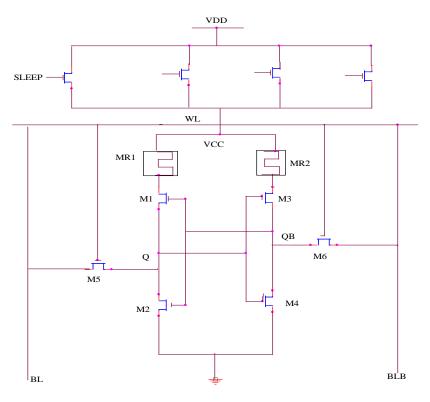

In a READ operation, WL = 1, and so M5 and M6 transistors arein ON condition. Both the BL and BLB bits lines are pre-charged to logic 1.

Values stored in Q and QB are transferred to the bit lines by leaving BL to its pre-charged value and at the same time discharging BLB to logic 0. Assuming that the voltage falls on transistors are negligible, the maximum voltage applied to M1 or M2,  $V_{Write}$ , must satisfy the following equation (1).

Figure 1: APSO Technique employed 6T-2M Memristor based SRAM

$Vwrite > V_{SET} and V_{RESET}$ (1)

Hence the proposed work minimizes this leakage current, with the technique of sleep which considers high threshold voltage transistor that can be nMOS.

## 3.1. Absolute Path Search Optimization (APSO) Algorithm

Among write task, if there is a hit from anyway, at that point the set relating to that specific way will be chosen with the assistance of list.

Pseudo Code of write mode:

Input: Write Sequence Ws (Match Line sensing)

Output: Stored Pattern Set Ps.0, 1, x

Start

Write the bit of sequence Bs.

$Bs = \int size(Ws)$

For each cell Ci from Bs

Store the Pattern Si.

$Si = \int_{i=1}^{Bs} Subset(Ws, Ci)$

Add to pattern set Ci.

$$\operatorname{Ci} = \sum_{i=0}^{n} W(0) \in W(1)) \cup Bs$$

End

International Journal of Psychosocial Rehabilitation, Vol. 23, Issue 03, 2019 ISSN: 1475-7192

If pattern Ci = '1' then Send single block write command Else Send multi-block write command End if If received response = 'True' then Go to decision process Else Stop.

While reading the cache all the four different ways will be empowered. The set, from where the information must be read, is chosen, with the assistance of list bits separated from the address bits originating from the processor.

Input: Cell Pattern Set Ps, Pattern Pi (Search line sensing)

Output: Search word or sequence. S Out

Start

Step 1: Put on search key.

Step 2: Distribute search key into N substitute words.

Step 3: Entirely layers custom algorithm 1 in parallel. S

Step 4: Get Match Address (MA) among Potential Match Address (PMAs) /divergence occurs

Step 5: If all PMAs authenticate their consistent sub words

For each cell l from Ps

Step 6: Calculate similarity.

$$S_{\text{Out}} = \int_{i=1}^{\text{cells}} \int_{j=1}^{\text{size}(Ps)} \sum Ps(j,l) = Pl$$

Where i = Number of Memory Bits

j = total size data

Step 7:  $S1out = \frac{Sout}{size (cells)}$

Step 8: Else

Mismatch occurs End If

Stop

#### **IV. SIMULATION RESULTS**

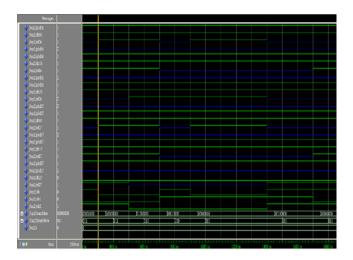

This section discusses the simulation results and performance analysis of the proposed APSO based MeTCAM. The performance of the proposed MeTCAM system is validated through simulation using Xilinx14. The following figure and tables show the simulation results and performance analysis of the proposed system.

Figure 1: Matched results of MeTCAM

The data search operation of the proposed deep search pattern based MeTCAM simulation result are shown in Figure.3. This simulation result clearly demonstrates that the searched data are available inside the MeTCAM cells and marked in blue lines.

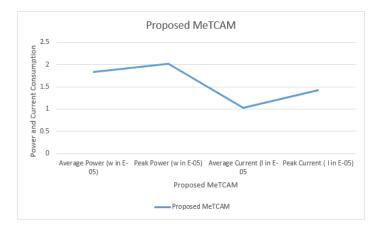

Figure 4 represents the average current, peak current, average power and peak power consumption of the proposed

Figure 2: Power and Current Consumption Analysis

APSO Method based MeTCAM system. By using APSO Method, the overall response of the current and power consumption is low.

## **V.** CONCLUSION

This section proposes a hybrid structure for a ternary CAM (TCAM) that utilizes two Transistors and memristors to defeat all issues. The proposed TCAM memory cell is researched concerning a few features, such as resistance and voltage range of the memristor. A farreaching simulationbased assessment of this TCAM is developed using Xilinx programming language utilizing APSO Method. The Simulation work exhibits that the execution of the

proposed algorithms is better than the past methods for improving the performance of search applications. An Overall efficiency of 97.5% was achieved by using this proposed system.

# REFERENCES

- [1] N. Vijaykumar, Reactive-associative caches, *In Proc. Int. Conf. Parallel Arch. Compiler Tech.*, 2011, p. 4961.

- [2] J. Dai and L. Wang, "Way-tagged cache: An energy-efficient L2 cache architecture under write-through policy," *In Proc. ISLPED*, 2009, pp. 159–164.

- [3] F. X. Ruckerbauer and G. Georg akos, "Soft error rates in 65 nmSRAMs: Analysis of new phenomena," *In Proc. IEEE Int. On-LineTest. Symp.*, 2007, pp. 203–204.

- [4] G.H. Asadi, V. Sridharan, M.B. Tahoori, and D. Kaeli, "Balancing performance and reliability in the memory hierarchy," *In Proc. Int. Symp. Perform. Anal. Syst. Softw.*, 2005, pp. 269–279.

- [5] X. Vera, J. Abella, A. Gonzalex and R. Ronen, "Reducing of error vulnerability of data caches," *Presented at the Workshop System Effects Logic Soft Errors*, Austin, TX, 2007.

- [6] P. Kongetira, K. Aingaran, and K. Olukotun, "Niagara: A 32-way multithreaded Sparc processor," *IEEE Micro*, vol. 25, no. 2, pp. 21–29, Mar. 2005.

- [7] X. Vera, J. Abella, A. Gonzalez and R. Ronen, "Reducings of error vulnerability of data caches," presented at the Workshop System Effects Logic Soft Errors, Austin, TX, 2007

- [8] J.S. Yadav, M. Yadav, and A. Jain, "CACHE MEMORY OPTIMIZATION," International Conferences of Scientific Research and Education, vol. 1, no. 6, pp. 1–7, 2013.

- [9] H. Dybdahl, "Architectural Techniques to Improve Cache Utilization" Diss. Ph.D. thesis, Norwegian University of Science and Technology, 2007.

- [10] X. Ding and K. Wang, "ULCC: A User-Level Facility for Optimizing Shared Cache Performance on Multicores." *ACM big plan notices*, Vol. 46, No. 8, ACM, 2011.

- [11] S. Paper, R. Sawant, B. H. Ramaprasad, S. Govindwar, and N. Mothe, "Memory Hierarchies-Basic Design and Optimization Techniques Survey on Memory Hierarchies – Basic Design and Cache Optimization Techniques," 2010.

- [12] M. Zhang and K. Asanovic, "Highly-Associative Caches for Low-Power Processors", *Appears in Kool Chips Workshop, 33rd Int. Symp. on Microarchitecture,* 2000.

- [13] M. Horowitz, "Computing's energy problem (and what we can do about it)," In Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2014, pp. 10–14.

- [14] H. Topcuoglu, S. Hariri, and M.-Y. Wu, "Performance-effective and low complexity task scheduling for heterogeneous computing," *IEEE Trans. Parallel Distrib. Syst.*, vol. 13, no. 3, pp. 260–274, Mar. 2002.

- [15] D. Xie, J. Lai, and J. Tong, "A high utilization rate routing algorithm for modern FPGA," *In Proc. 9th Int. Conf. Solid-State Integr.-Circuit Technol. (ICSICT)*, Oct. 2008, pp. 2333–2336.

- [16] Deepa A., Marimuthu C.N., "Study of Reed Solomon encoders and its architectures", *International Journal of Applied Engineering Research*, Volume 9, Issue 20, Pages 6855-6862, 2014.

- [17] Jerin Jose, M., Akmal Jahan, S., Arunachalam, R., Karnan, R., & Kishore, V. (2017). Automobile Accident Sensing Unit and Notifier using Arduino. *The SIJ Transactions on Industrial, Financial & Business Management (IFBM)*, 5(1), 5-8

- [18] RAJAN C., SHANTHI N.(2015). Genetic based optimization for multicast routing algorithm for MANET. *Sadhana Academy Proceedings in Engineering Sciences*, 40(8).

- [19] Prabhadevi S., Javavel S., Kapoor R.(2015). Algorithm of sentiment analysis for computing machines. *Journal of Scientific and Industrial Research*, 74(12).

- [20] Palanisamy T., Krishnasamy K.N.(2015). Bayes node energy polynomial distribution to improve routing in wireless sensor network. *PLoS ONE*, 10(10).

- [21] Prasath A., Satheesh A.(2015). Implementation of real time data acquisition system with ARM. *ICIIECS* 2015 2015 IEEE International Conference on Innovations in Information, Embedded and Communication Systems.

- [22] Gokula Krishnan, C.A., & Dr. Suphalakshmi, A. (2017). An Improved MAC Address Based Intrusion Detection and Prevention System in MANET Sybil Attacks. *Bonfring International Journal of Research in Communication Engineering*, 7(1), 1-5.

- [23] Balakrishnan M., Gowthaman S., Jaya Kumaran S.P., Sabhapathy G.R.(2015). A smart spy robot charged and controlled by wireless systems. *ICIIECS 2015 2015 IEEE International Conference on Innovations in Information, Embedded and Communication Systems.*

- [24] Sasikala E., Rengarajan N.(2015). An Intelligent Technique to Detect Jamming Attack in Wireless Sensor Networks (WSNs). *International Journal of Fuzzy Systems*, 17(1).

- [25] Gopinath B., Shanthi N.(2015). Development of an automated medical diagnosis system for classifying thyroid tumor cells using multiple classifier fusion. *Technology in Cancer Research and Treatment*, 14(5).

- [26] Ravikumar P., Arumugam S., Jeyashanthi N. (2016). Computational modeling of amperometric choline biosensor for neurochemical detection. *Biomedical Research (India)*, 27(4).

- [27] Kurian, S., & Franklin, R.G. (2013). Trustworthy Coordination of Web Services Atomic Transaction for Net Banking. *The SIJ Transactions on Advances in Space Research & Earth Exploration*, 1(1), 6-9.

- [28] Ramani G., Geetha K. (2016). An efficient code compression for MIPS32 processor using dictionary and bit-mask based static and dynamic frequency algorithm. *COMPEL The International Journal for Computation and Mathematics in Electrical and Electronic Engineering*, 35(5).

- [29] Ravi S., Mezhuyev V., IyswaryaAnnapoorani K., Sukumar P. (2016). Design and implementation of a microcontroller based buck boost converter as a smooth starter for permanent magnet motor. *Telkomnika* (*Telecommunication Computing Electronics and Control*), 1(3).

- [30] Gnanambigai J., Rengarajan N. (2016). A novel approach to enhance the network lifetime for hybrid routing protocol. *International Journal of Information and Computer Security*, 8(2).

- [31] KarthickRaghunath K.M., Rengarajan N. (2016). A novel fuzzy integrated fault-tolerant and energyefficient routing protocol for Wireless Sensor Network. *Asian Journal of Information Technology*, 15(8).

- [32] Vijayalakshmi M. (2016). Synthesis, spectral characterization, biological activity and dna cleavage studies of cu(Ii), ni(II) AND zn(II) SCHIFF base complexes derived from 2,4-dihydroxy benzaldehyde and p-chloroaniline. *International Journal of ChemTech Research*, 9(3).

- [33] Sukumar P., Gnanamurthy R.K.(2016). Computer aided screening of cervical cancer using random forest classifier. *Research Journal of Pharmaceutical, Biological and Chemical Sciences*, 7(1)

- [34] Kumar, V., &Balasubramanie, P. (2007). Implementation of Modified MAC Based Pipelining Technique for Wireless Networks. *Information Technology Journal*, 6(8), 1231-1237.

- [35] Sengottaiyan, N., Somasundaram, R., & Arumugam, S. (2009). A modified routing algorithm for reducing congestion in wireless sensor networks. *European Journal of Scientific Research*, *35*(4), 529-536.

- [36] Suresh, Y., Arumugam, S., Chandrasekaran, M., Senthilkumar, J., &Mohanraj, V. (2009, October). A QSPS-PSR Approach on Differentiated TCP Flows for Internet Traffic. In 2009 International Conference on Advances in Recent Technologies in Communication and Computing (pp. 263-265). IEEE.

- [37] Dr. Gopinath, B., Kalyanasundaram, M., Karthika, V., & Pradeepa, M. (2018). Development of Power Quality Event Using Diode Clamped Multilevel Inverter in Conjunction with AANF. *Bonfring International Journal of Software Engineering and Soft Computing*, 8(1), 17-22.

- [38] Ashok, V., Kumar, A. N., Kumar, S. S., &Kasthuri, N. (2010). Continuous wavelet transform analysis of blood flow for the determination of hyper and hypo glycemic conditions. *Procedia Computer Science*, *2*, 291-297.

- [39] Sagayee, G. M. A., &Arumugam, S. (2010, February). Biometric image enhancement using decision rule based image fusion techniques. In *Second International Conference on Digital Image Processing* (Vol. 7546, p. 75463F). International Society for Optics and Photonics.

- [40] Sivakumar, V., Sivasankaran, S., Prakash, P., & Lee, J. (2010). Effect of heating location and size on mixed convection in lid-driven cavities. *Computers & Mathematics with Applications*, 59(9), 3053-3065.

- [41] Nirmaladevi, M., & Arumugam, S. (2010). VLSI Implementation of Artificial Neural Networks— Asurvey. *International Journal of Modelling and Simulation*, 30(2), 148-154

- [42] Kavitha, S., &Duraiswamy, K. (2011). Automatic detection of hard and soft exudates in fundus images using color histogram thresholding. *European Journal of Scientific Research*, 48(3), 493-504.

- [43] Ravi, S., &Balakrishnan, P. A. (2011). Dual screw profile extruder temperature control using LabVIEW enhanced Genetic Fuzzy Algorithm. *European Journal of Scientific Research*, *50*(1), 35-47.

- [44] Mohanraj, V., Chandrasekaran, M., Senthilkumar, J., Arumugam, S., & Suresh, Y. (2012). Ontology driven bee's foraging approach based self adaptive online recommendation system. *Journal of Systems and Software*, 85(11), 2439-2450.

- [45] Suresh, Y., Arumugam, S., &Bhagyaveni, M. A. (2012). A Forager Bee's Intelligence Inspired Dynamic Queue Scheduling for the Internet Traffic. *Journal of Computer Science*, 8(5), 665.

- [46] Saravana, K. T., &Sampath, V. (2011). An Artificial Neural Network System for Prediction of Dimensional Properties of Weft Knitted Rib Fabric. *Journal of the Textile Association*, 71(5), 247-250.

- [47] Vijayakumar, J., & Arumugam, D. S. (2012). Study of betelvine plants diseases and methods of disease identification using digital image processing. *European Journal of Scientific Research*, 70(2), 240-244.

- [48] Satheesh, A., & Manigandan, T. (2012). Improving power system stability using PSO and NN with the aid of FACTS controller. *European Journal of Scientific Research*, 71(2), 255-264.

- [49] Rameshkumar, A., &Arumugam, S. (2012, April). PI Control of Quasi-resonant Buck Converter. In *International Conference on Advances in Information Technology and Mobile Communication* (pp. 477-485). Springer, Berlin, Heidelberg.

- [50] Suresh, Y., Arumugam, S., &Bhagyaveni, M. A. (2012). A Forager Bee's Intelligence Inspired Dynamic Queue Scheduling for the Internet Traffic. *Journal of Computer Science*, 8(5), 665.

- [51] Ramesh, K., &Somasundaram, K. (2012, January). Optimized FZ-LEACH Using Exponential Weighted Moving Average for Wireless Sensor Network. In *International Conference on Computer Science and Information Technology* (pp. 473-481). Springer, Berlin, Heidelberg.

- [52] Satheesh, A., & Manigandan T. (2013). Maintaining Power System Stability with Facts Controller Using Bees Algorithm and NN. *Journal of Theoretical and Applied Information Technology*, 49 (1), 38-47.

- [53] Vijayalakshmi M., &Subramanian P. Synthesis, spectral characterization, biological activity and DNA cleavage studies of Cu(II), Ni(II) and Zn(II) schiff base complexes derived from 2,4-dihydroxy benzaldehyde and P-aminophenol. *International Journal of Pharmacy and Technology*, 5(1):5144-5155.

- [54] Prabhadevi, S., De, R., & Shah, P. (2013). Cost Effective Poly Vernam Cipher with Cache Optimization. *Journal of Theoretical & Applied Information Technology*, 58(3).

- [55] Dr. Chaturvedi, A., Bhat, T.A., & Kumar, V. (2013). Movement based Asynchronous Recovery System in Mobile Computing System. *The SIJ Transactions on Computer Networks & Communication Engineering* (*CNCE*), 1(3), 1-5.

- [56] Prabhadevi S., &Natarajan A.M. (2013). Vehicular ad hoc networks: Characteristics, application and standards. *Asian Journal of Information Technology*, 12 (11): 387-390.